## **High-K Dielectrics in Nano&Microelectronics**

G. BREZEANU<sup>1</sup>, M. BREZEANU<sup>2</sup>, F. BERNEA<sup>3</sup>

<sup>1</sup>University "POLITEHNICA" Bucharest, Splaiul Independentei 313, 040011, Bucharest, Romania <sup>2</sup>Engineering Department, University of Cambridge, 9 JJ Thomson Avenue, Cambridge CB3 0FA, UK <sup>3</sup>Carpatcement Holding, Romania

**Abstract.** For CMOS applications, as device scaling, obeying Moore's law reduces the active area of the devices to nearly atomic dimensions. The high-k dielectrics need to be used to prevent the tunnelling effects which increase the leakage currents. These insulators are also important for enabling high-performance nanoelectronic transistors built on high-mobility materials, such as diamond, carbon nanotubes or silicon carbide (SiC).

One of the major issues to be addressed when coming to power devices is the choice of the appropriate termination. An already, classical implementation of the field plate technique, widely used for Si, SiC and diamond power diodes, is the oxide ramp termination. This method requires the presence of a dielectric ramp smaller than 10°, etched around the anode, which assures the smoothness of the electric field at the contact's periphery. The main limitation of this termination is a premature oxide breakdown which is a killing factor for the yield. The paper presents improvements in the efficiency of this termination for Schottky Barrier Diodes (SBDs) on SiC and diamond, using high-k dielectrics. These insulators can reduce both the oxide and the surface semiconductor electric field.

## Introduction

In recent years, several emerging high-k materials have attracted enormous attention as potential candidates for electronic devices. Silicon dioxide (SiO<sub>2</sub>) has been used as dielectric for more than 40 years because of its manufacturability and ability to deliver continued transistor performance improvements as it has been made ever thinner [1-10].

Over decades of incremental improvements to CMOS processing, the limitations of the  $SiO_2$  gate dielectric layer have hung over the silicon industry as its single biggest technical challenge [1-15]. To improve MOS transistor

performance in the past, chip manufacturers have shrunk the thickness of the gate dielectric to as little as five atomic layers (1.2 nm). Although this has helped transistors reach very high speeds, the problem is that these very thin layers of  $SiO_2$  tend to leak a lot of current, resulting in energy waste and a build-up of heat. In addition,  $SiO_2$  thickness uniformity across a 12 inch wafer imposes even more crucial difficulty in the growth of such a thin film, since even a mono-layer difference in thickness represents a large percentage difference and thus can result in the variation of threshold voltage across the wafer [4]. Reliability also becomes a huge concern for a very thin layer  $SiO_2$  film.

Intel have been integrated into a manufacturable 45nm process a combination of a high-k dielectric based on hafnium and a new metal gate material compatible with hafnium will reduces source-drain leakage substantially [1,9-10]. Gordon Moore described this new approach, as the *"biggest change in transistor technology since the introduction of polysilicon gate MOS transistors in the late 1960s"*[10].

IBM has come up with a slightly different solution to the leakage problem, but is also using a high-k dielectric gate, [10]. The latest developments at Intel and IBM will help III-V devices penetrate new markets, by instigating greater convergence of the compound and silicon industries. High-k dielectric is at the centre of this, and high-k compound semiconductor MOSFETs will be able to leverage the millions of man years of silicon circuit designs, [10].

Actually, there is an increasing interest in the use of wide band-gap semiconductors, such as silicon carbide (SiC) and diamond, for power switching, power conversion, motor drives and military and consumer electric vehicles [16-22]. An issue related to the design of SiC or diamond devices is the junction discontinuity at the sharp corners of the electrodes. These results in noticeable increase of the maximum electric field in semiconductor bulk compared with its one dimensional value. These field peaks can be reduced using edge terminations surrounding the electrodes periphery [16-17]. Field plate termination is widely used in power devices design due to a less complicated fabrication process. We proposed and already tested on Si, SiC and diamond diodes a simple, low temperature, field plate termination based on a small angle etching of a dielectric deposed around the anode contact [18-22].

The paper presents enhancements in this termination for Schottky barrier diodes (SBDs) on SiC and diamond, using high-k dielectrics. The use of high-k materials allows for the reduction of the electric field at the corner by minimizing the recess without losing electrode control.

### Scaling limits of SiO<sub>2</sub>

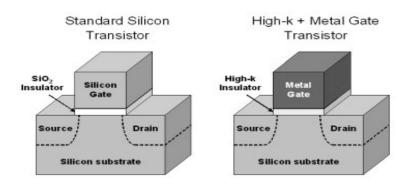

The prosperity of modern integrated circuits has been realized with continuous shrinkage of MOS transistors (Fig. 1). Miniaturization of transistors has not only

increased package densities, but also accelerated circuit speed and reduced power dissipation [1-15].

Fig. 1. MOS transistor structure with dielectric gate [10].

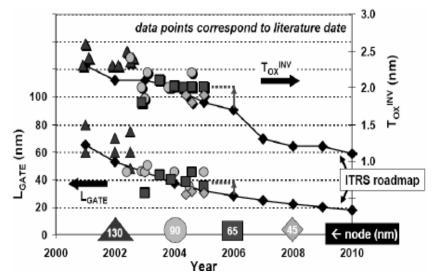

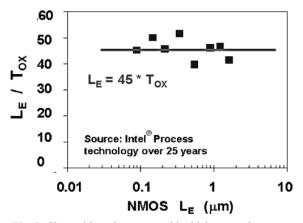

These improvements were achieved by scaling down of physical thickness of the gate dielectric ( $T_{ox}$ ) and gate length ( $L_{GATE}$ ). As shown in Fig.2, scaling of  $L_{GATE}$  and  $T_{ox}$  is slowing with technology nodes [6]. Fig. 3 plots channel length divided by gate oxide thickness for Intel's process technologies over the past 20 years [6]. Each data point represents a process technology, which was used to fabricate Intel's leading-edge microprocessors. A simple relationship between oxide thickness and the minimum channel length set by short channel effects is observed. Thermally grown silicon oxide (SiO<sub>2</sub>) has been used as gate dielectric because it offers many desirable properties such as: an excellent interface, thickness controllability, high thermal stability and good reliability [2-4].

Fig. 2. Scaling trend of gate length and oxide thickness (ITRS International Technology Roadmap for Semiconductors) [6].

Fig. 3. Channel length to gate oxide thickness ratio versus channel length for some Intel process technologies [6].

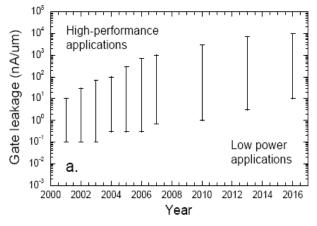

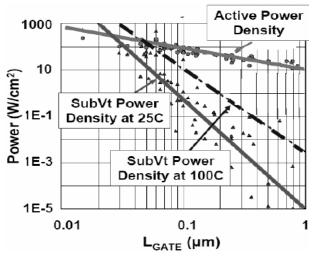

For new CMOS nanotechnology ( $L_{GATE}$ < 90nm) SiO<sub>2</sub> has reached its physical limitations: higher leakage current and reliability concerns. A physical thickness of 11-15Å is so thin that electrons can directly tunnel through the oxide, resulting in excessively high gate leakage current. The forecasted leakage current is shown in Fig. 4 [5]. High leakage is a great concern, particularly for low power requests, and high performance applications as well. Due to the increase in the gate leakage, static power can exceed the active power as shown in Fig. 5, [6]. To reduce the increase in active power,  $V_{DD}$  needs to be reduced as well.

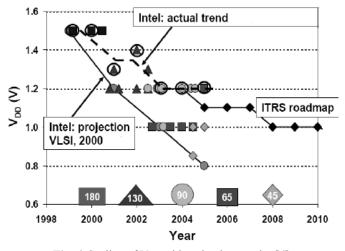

But as seen in Fig. 6 [6],  $V_{DD}$  is also falling behind the roadmap targets thus limiting the reduction of active power and increasing the electric field across the gate oxide, which decreases the reliability of the gate oxides.

**Fig. 4.** The predicted range of acceptable gate leakage current over the years; the upper limit represents high performance and the lower limit represents low power applications [5].

Fig. 5. Active and static power increase with scaling of  $L_{GATE}$ .

Fig. 6. Scaling of V<sub>DD</sub> with technology nodes [6].

# High-k dielectrics

High-*k* gate dielectrics have been studied as alternative gate dielectrics for the 65nm CMOS technology (Fig. 1) and beyond to replace conventional  $SiO_2$  or silicon oxynitrides ( $SiO_xN_y$ ). The requirements for high-k dielectric applications are [5]:

- ✤ high dielectric constant and large band gap

- high band offset with electrodes

- thermally and chemically stable in contact with semiconductor substrate

- \* scalable equivalent oxide thickness EOT < 10Å

- compatibility with gate electrode material

- density of interface states comparable to SiO<sub>2</sub>

- Iow lattice mismatch and similar thermal expansion coefficient with Si

- $\bigstar$  mobility comparable to SiO<sub>2</sub>

- negligible capacitance-voltage hysteresis (< 20mV)</li>

- \* good reliability (no charge trapping, high breakdown voltage etc.)

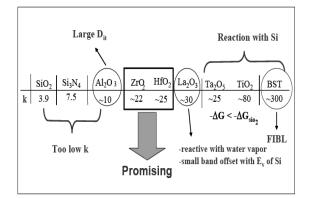

In Fig. 7, dielectric constants of high-k candidates were summarized [4, 11-14]. TiO<sub>2</sub> and barium strontium titanate (BST) showing profoundly higher permittivity, were reported not to be thermally stable with silicon substrates [4]. It is worth mentioning that high-k dielectrics such as BST do not seem to be appropriate since the very high dielectric constant causes field induced barrier lowering (FIBL) which degrade short channel effects of MOS transistor [4]. A high density of surface states has been reported for Al<sub>2</sub> O<sub>3</sub>.

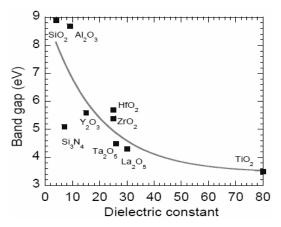

In general, with the increase of the metal atomic number, the metal ionic radius increases, but the cohesive force decreases in the metal oxide, and results in a large dielectric constant. The bandgap energy decreases related to the dielectric constant [8].

$$E_G \Box \left(\frac{3}{2+\varepsilon_k}\right)^2 \tag{1}$$

Fig. 8 shows the bandgap and dielectric constant of some dielectric materials [7]. The inverse relationship suggested by above Eq. (1) is clearly demonstrated.

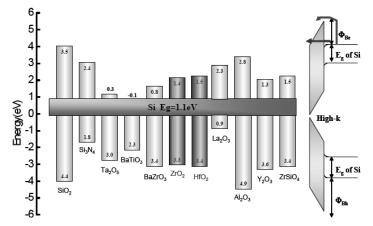

A narrow bandgap results in smaller energy band offsets with Si. Band offsets of high-k dielectrics with the conduction band edge ( $\Phi_{Be}$ ) and valence band edge  $\Phi_{Bh}$  of Si is compared in Fig. 9 [4, 15]. The higher band offset indicates that the carrier generation and conduction can be minimized. A band offset less than 1.0 eV may lead to an unacceptably large leakage current. This current is more likely to be governed by direct tunneling current given by [4]:

$$J_{e(h)} = \frac{A}{T_k^2} \left[ \left( \Phi_{Be(h)} - \frac{V}{2} \right) \cdot \exp\left( BT_k \sqrt{\Phi_{Be(h)} - \frac{V}{2}} \right) - \left( \Phi_{Be(h)} + \frac{V}{2} \right) \cdot \exp\left( BT_k \sqrt{\Phi_{Be(h)} + \frac{V}{2}} \right) \right]$$

(2)

where:

$$A = \frac{q^2}{2\pi h} \qquad B = \frac{4\pi}{h} \sqrt{2m^* q}$$

$T_k$  is dielectric thickness and q,  $m^*$ , and h represent electron charge, effective mass of electron, and Plank's constant, respectively. Therefore, the leakage current depends significantly on band offsets and to oxide thickness. Based on the band offset in Fig. 9,  $Ta_2O_5$ , which has been studied widely for the application in DRAM storage capacitors appears to be unsuitable for the gate electrode application. Al<sub>2</sub>O<sub>3</sub> and Si<sub>3</sub>N<sub>4</sub> have too low *k* to be used for several generations as shown in Fig.7-9. Among these materials, HfO<sub>2</sub> has been shown to be compatible with: poly-silicon gate, poly-SiGe and TaN gates [4]. In contrast, ZrO<sub>2</sub> has been reported that it was not compatible with poly-Si gate due to the reaction of Zr with poly-Si gate [4].

If a high-k dielectric can replace  $SiO_2$ , the dielectric thickness ( $T_k$ ) increases proportionally to keep the same dielectric capacitance. A figure of merit to judge a high-k gate dielectric layer is the equivalent oxide thickness, defined as [2-8]

$$EOT = \frac{\varepsilon_{ox}}{\varepsilon_k} T_k \tag{3}$$

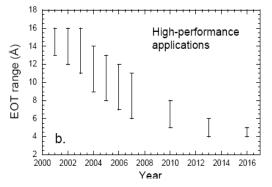

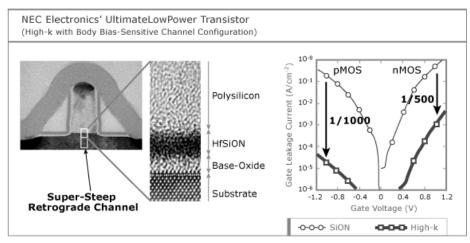

where  $\varepsilon_{\alpha x}/\varepsilon_k$  is the ratio of relative oxide and high-k dielectric permittivity, respectively. Since a thicker layer is used for insulating, the tunneling current is drastically reduced. However, a new high-k material can be integrated into the present ULSI process. In Fig.10 the expected EOT evolution for these processes is shown [5]. The upper limit corresponds to high performance and the lower limit denotes low power applications [5]. MOSFETs with HfO2 dielectrics and TaN gate showed very low EOT and low leakage current even after the conventional CMOS process flow [9-10]. Considering the cost of development and implementation,  $HfO_2$  gate dielectric needs to span two or three generations from the 65 nm to the 32 nm design rule. To meet the requirements for these generations, EOT should be scaled down to less than 10A while suppressing leakage current to below  $1 \text{mA/cm}^2$ (Fig. 11), [9]. A combination of a high-k dielectric based on hafnium and a secret new metal gate material compatible with hafnium will cut gate leakage current density by more than 500 times (Fig. 11). The dielectric's high k value compensates for the thinning of the dielectric in smaller process geometries. A thinner dielectric enables higher drive and thus allows transistors to switch faster.

Fig. 7. Dielectric constant of some high-k dielectrics [4,11-14].

**Fig. 8.** Band gap dependence versus dielectric constant of some high-k dielectrics [4,11-14.

Fig. 9. Band offset of gate dielectric candidates with conduction band edge and valence band edge of Si substrate [4,15].

Fig. 10. The predicted evolution of equivalent oxide thickness [5].

Fig. 11. Nano- MOS structure with high-k dielectric [9].

## SiC and Diamond Electronics Devices With High-k Dielectrics

Wide band gap semiconductors such as diamond and SiC are the promising materials for new power devices. Over the last two decades, significant advances in the growth, doping, and processing technologies of these materials have been accomplished opening new promise for high power electronics. In real devices, the breakdown voltage of the devices is always less than that predicted by theory, since the material is not perfect (crystal defects) and the electric field is crowding at the electrode corner [16-22].

These high fields can be relieved by using edge termination surrounding the electrode periphery. An effective edge termination makes the electric field distribution uniform in the bulk and at the electrode corner and take the breakdown capability of the device closer to its theoretical limit. Traditionally, techniques like field plates, floating guard rings and junction termination extensions have been used [16-17].

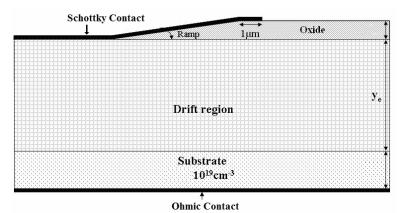

We have already proposed the oxide ramp termination, an original implementation of the field plate concept, previously widely used for Si, SiC and diamond (Dia) diodes. This termination, shown in Fig. 12 for a Schottky Barrier diode (SBD), is based on a field plate overlapping on oxide ramp at the periphery of the device main electrode contact. The oxide ramp termination is acknowledged by the international community as a highly efficient termination for power devices [16-22]. In this paper, the high-k insulators are used with the ramp oxide termination of SiC and diamond diodes.

For power devices, due to the high voltages employed, the dielectric breakdown might appear before the semiconductor one. The use of alternative insulators, with high dielectric constants will reduce the electric field within the oxide and, as a consequence, the risk of premature dielectric breakdown. In order to emphasize the effect of varying the relative permittivity ( $\varepsilon_r$ ) on the performance of ramp oxide terminated structures, extensive simulations were performed on SiC and diamond diodes. In order to avoid dielectric breakdown, the maximum electric field in the oxide ( $E_{OX}$ ), has to be lower than 5-6MV/cm, acceptable operating fields for high-*k* dielectrics like Si<sub>3</sub>N<sub>4</sub>, Ta<sub>2</sub>O<sub>5</sub> or HfO<sub>2</sub> (the later having the highest product between the dielectric constant and the maximum electric field). The increase of  $\varepsilon_r$  not only reduces  $E_{OX}$ , but also improves the breakdown voltage (BV) of the diodes. The termination efficiency ( $\eta$ ), defined as the ratio between the achieved BV and the ideal one, significantly increases for larger  $\varepsilon_r$ , regardless of the ramp angle.

Fig. 12. Schottky barrier diode (SBD) with oxide ramp termination.

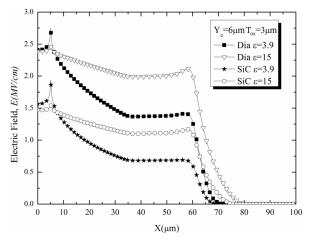

Fig. 13 presents the electric field distribution at the semiconductor surface for both SiC and Dia SBDs, having the same doping level in the drift layer  $(7x10^{15}cm^{-3})$ . Two peaks, are observed: one at the beginning and one at the end of the ramp. For both materials, the increase of  $\varepsilon_r$  results in a severe reduction of the field peak at the start of the ramp. An increase of the overall electric field at the interface and, a smooth electric field distribution at the Schottky contact and along of the oxide-semiconductor interface can be observed at higher permittivity. This is due to the increase of the voltage drop on the semiconductor when insulators with high permittivity are used.

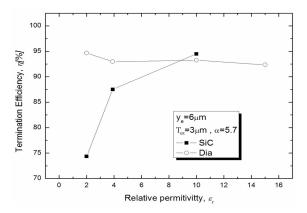

Consequently, an increase of the termination efficiency is obtained. For SiC SBDs, the efficiency of termination increases strongly with  $\varepsilon_r$ , up to 96% (Fig.14). In the case of Dia, the effect of the insulator permittivity is reduced, mainly due to the much lower doping of the drift layer (used in these simulations), and the termination efficiency is around 92%. A mild decrease of the efficiency is observed for high permittivity value.

Fig. 13. Electric field along the interface Dia and SiC SBDs with the same drift doping.

Fig. 14. Termination efficiency vs. dielectric relative permittivity for SiC and Dia SBDs.

Another important benefit of the relative permittivity growth is that the ramp angle can be increased up to  $10^{0}$ , without affecting the value of the efficiency. This has a direct influence on the area consumption, taking into account the fact that the larger the angle, the smaller the area needed for the termination.

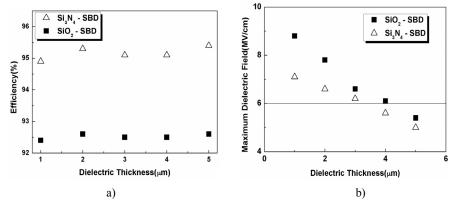

In order to confirm the predictions of the theoretical study presented above, a comparison between the performances of the Schottky diodes, when employing  $SiO_2$  and  $Si_3N_4$  as insulators for the ramp termination, was performed in Fig.15.The ramp angle was kept constant (5.7<sup>o</sup>), while the thickness of the dielectric was varied in the range 0.5-5µm. The  $Si_3N_4$  ramps show better performances both in terms of termination efficiencies and maximum electric field in insulator (Fig. 15). A very high efficiency of 95% can be obtained for this diode using the silicon

nitride for ramp termination (Fig. 15a). The fact that  $\eta$  is very high and practically constant with  $T_{OX}$ , enables the design to be focused only on reducing  $E_{OX}$ , which falls below the acceptable maximum for thicknesses larger than 3.5µm (Fig. 15b).

**Fig. 15.** Comparison between SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> SBDs on SiC from the point of view of (a) termination efficiency and (b) maximum electric field in the dielectric.

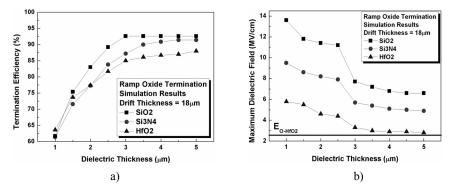

We have also analyzed the impact of using two high-*k* dielectrics, (Si<sub>3</sub>N<sub>4</sub> and HfO<sub>2</sub>), as insulators for the ramp termination on diamond Schottky structures (Fig.16). As expected, the electric field in the dielectric decreases at breakdown when using high-*k* dielectrics (Fig.16b). Values of the maximum dielectric field comparable to the operational field are obtained for HfO<sub>2</sub> ramps with insulator thicknesses in excess of 3.5  $\mu$ m. For these structures, the risk of premature dielectric breakdown is minimum. The price to pay for this improvement in reliability is a small degradation of the electrical performances of the termination. The efficiency drops by 5–7% to 85–87% when using HfO<sub>2</sub> instead of SiO<sub>2</sub> (Fig.16a), still high enough for a competitive termination structure.

**Fig. 16.** Oxide ramp termination with SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub> and HfO<sub>2</sub> for SBDs on diamond (a) termination efficiency and (b) maximum electric field in the dielectric.

### Conclusions

The requirement of high performance, high reliability, high package density along with low voltage and low power application for submicron CMOS technology and device scaling has acted as the driving force. A continuing scaling down of the MOS device with the minimum feature size bellow 90 nm requires EOT less than 15 Å. A physical thickness of only some atomic layers of traditionally gate insulator (SiO<sub>2</sub>) creates several problems. Electrons can directly tunnel through the SiO<sub>2</sub>, resulting in excessively high gate leakage current. To solve this critical issue SiO<sub>2</sub> has been replaced with a thicker high-*k* material as HfO<sub>2</sub> in the gate dielectric, clamming reduction in leakage by more than two orders of magnitude.

The possibility of using high-k dielectrics for field plate terminations of Schottky on SiC and diamond in order to avoid a possible premature dielectric breakdown was investigated, too.

A high efficiency oxide ramp termination based on high-k insulators has been extensively studied. For SiC SBDs, the efficiency of termination increases strongly with relative permittivity, up to 96%. In the case of Dia, the effect of the insulator permittivity is less significant, and the termination efficiency is around 92%.

With an HfO<sub>2</sub> ramp, the premature dielectric breakdown risk can be avoided for dielectric thicknesses larger than 3.5  $\mu$ m for diamond and SiC Schottky devices. A comparison between SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> ramps for SBDs on SiC showed that the latter exhibits superior performances.

In conclusion, high-k dielectrics are highly recommended for SiC devices, but have a lower impact in the case of low doping diodes on diamond.

### References

- [1] MUSCULAR Ann Stafford, *Intel, IBM embrace high-k metal gates for 45nm*, Electronic Weekly, January 2007.

- [2] AGRAWAL R., Fabrication, Characterization and Hall Mobility Analysis of MOS Devices with Low K and High K Dielectric Materials, Thesis for degree of Master of Science in Electrical Engineering, University of Texas at Arlington, 2006.

- [3] OK I., A Study on Electrical and Material Characteristics of Hafnium Oxide with Silicon Interface Passivation on III-V substrate for Future Scaled CMOS Technology, PhD Dissertation, University of Texas at Austin, 2008.

- [4] KANG C., A study on the material and device characteristics of hafnium oxynitride MOSFETs with TaN gate electrodes, PhD Dissertation, University of Texas at Austin, 2004.

- [5] NIEH R.E., An evaluation of the electrical, material, and reliability characteristics and process viability of ZrO<sub>2</sub> and ZrO<sub>x</sub>N<sub>y</sub> for future generation MOS gate dielectric, PhD Dissertation, University of Texas at Austin, 2002.

- [6] AKBAR M.S., Process Development, Characterization, Transient Relaxation, and Reliability Study of HfO2 and HfSixOy Gate Oxide for 45nm Technology and Beyond, PhD Dissertation, University of Texas at Austin, 2005.

- [7] SCHAEFFER J.K., *Hafnium Dioxide Gate Dielectrics, Metal Gate Electrodes, and Phenomena Occurring at their Interfaces*, PhD Dissertation, University of Texas at Austin, 2004.

- YANG X., Issues In Front-End Engineering Of Cmos Nanoelectronics, PhD Dissertation, University of Texas at Arlington, 2007.

- [9] High-k Transistor, advanced process technology, NEC Electronics Corporation, 2005.

- [10] IBM and Intel make high-k gate breakthrough, Compound semiconductor net, 2007.

- [11] SHANNON R.D., Dielectric polarizabilities of ions in oxides and fluorides, J. Appl. Phys., 73(1), p. 348, 1993.

- [12] WILK G.D., WALLACE R.M. and ANTHONY J.M., Hafnium and zirconium silicates for advanced gate dielectrics, J. Appl. Phys., 15(1), p. 484, 2000.

- [13] EZHILVALAVAN S. and TSENG T., *Conduction mechanisms in amorphous and crystalline Ta*<sub>2</sub>*O*<sub>5</sub> *thin films*, J. Appl. Phys., **83**(9), p. 4797, 1998.

- [14] PARK Donggun, KING Ya-chin, LU Qiang, KING Tsu-Jae, HU Chnming, KALNITSKY Alexander, TAY Sing-Pin, and CHENG Chia-Cheng, *Transistor Characteristics with Ta<sub>2</sub>O<sub>5</sub> Gate Dielectric*, IEEE Electron Device Letters, 19, p. 441, 1998.

- [15] ROBERTSON John, Band offsets of wide-band-gap oxides and implications for future electronic devices, Journal of Vacuum Science & Technology B:Microelectronics and Nanometer Structures, 18(3), p. 1785, 2000.

- [16] TARPLEE M.C., MADANGAGLY V.P., ZHANG Q., SURDARSHAN T.S., Design Rules for Field Pate Edge Termination in SiC Schottky Diodes, IEEE Trans. El. Dev., 48, p. 2659, 2001.

- [17] SHERIDAN D.C., NIU G., MERRETT J.N., CRESLLER J.D., ELLIS C., TIN C.C., Design and Fabrication of Planar Guard Ring Termination for High Voltage SiC Diodes, Solid St. Electron., 44, p. 1367, 2000.

- [18] BREZEANU G., BADILA M., BREZEANU M., UDREA F., BOIANCEANU C., ENACHE I., DRAGHICI F., VISOREANU A., *Breakdown performances improvements of SiC diodes* using high-k dielectrics, in Proc. of the 28<sup>nd</sup> International Semiconductor Conference, p. 357, 2-4 Oct., Sinaia, Romania, 2005.

- [19] BREZEANU M., BADILA M., BREZEANU G., UDREA F., BOIANCEANU C., AMARATUNGA G.A.J., ZEKENTES K., An Effective Field Plate Termination for SiC Devices Based on High-k Dielectrics, in Proc. of International Conference on Silicon Carbide and Related Materials-ICSCRM, p. 21, 18-23 Sept, Pittsburg, USA, 2005.

- [20] BREZEANU M., AVRAM M., RASHID S.J., AMARATUNGA G.A.J., BUTLER T., RUPESINGHE N.L., UDREA F., TAJANI A., DIXON M., TWITCHEN D.J., GARRAWAY A., CHAMUND D., TAYLOR P., BREZEANU G., *Termination Structures for Diamond Schottky Barrier Diodes*, in Proc of the 18th International Symposium on Power Semiconductor Devices and ICs (ISPSD 2006), p. 73, 4-8 June, Napoli, Italy, 2006.

- [21] BREZEANU M., BUTLER T., RUPESINGHE N.L., AMARATUNGA G.A.J., RASHID S.J., UDREA F., AVRAM M., BREZEANU G., *Ramp Oxide Termination Structure using High-k Dielectrics for High Voltage Diamond Schottky Diodes*, Diamond and Related Materials, 16, p. 1020, 2007.

- [22] BREZEANU G., BREZEANU M., BOIANCEANU C., UDREA F., AMARATUNGA G.A.J., GODIGNON P., Impact of High-k Dielectrics on Breakdown Performances of SiC and Diamond Schottky Diodes, Material Science Forum, 600-603, p. 983, 2009.